Description

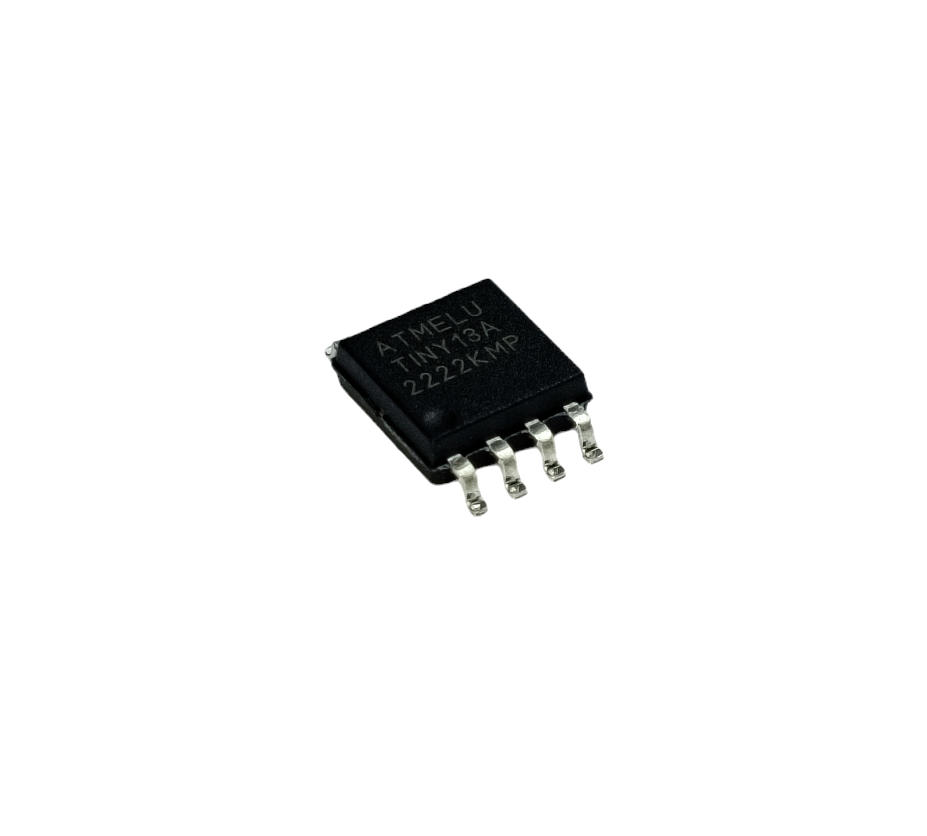

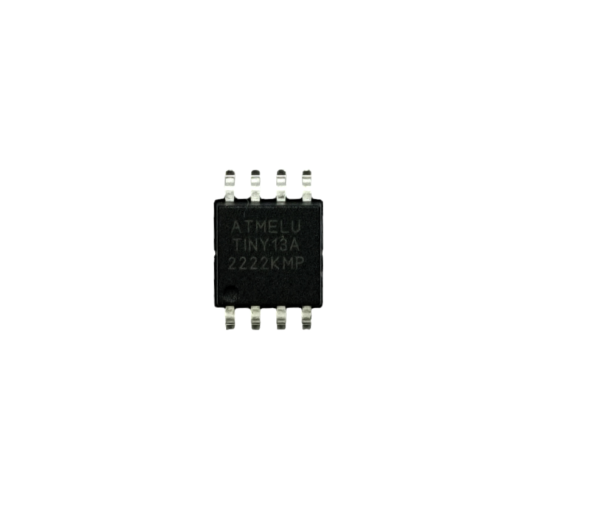

Product Overview

Microchip Tech ATTINY13A-SUR is a low-power CMOS 8-bit microcontroller based on the AVR® enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny13A achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

Features of Microchip Tech ATTINY13A-SUR

• High Performance, Low Power AVR® 8-Bit Microcontroller

• Advanced RISC Architecture

– 120 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 20 MIPS Througput at 20 MHz

• High Endurance Non-volatile Memory segments

– 1K Bytes of In-System Self-programmable Flash program memory

– 64 Bytes EEPROM

– 64 Bytes Internal SRAM

– Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 Years at 85C/100 Years at 25 Degrees C

– Programming Lock for Self-Programming Flash & EEPROM Data Security

• Peripheral Features

– One 8-bit Timer/Counter with Prescaler and Two PWM Channels

– 4-channel, 10-bit ADC with Internal Voltage Reference

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

• Special Microcontroller Features

– debugWIRE On-chip Debug System

– In-System Programmable via SPI Port

– External and Internal Interrupt Sources

– Low Power Idle, ADC Noise Reduction, and Power-down Modes

– Enhanced Power-on Reset Circuit

– Programmable Brown-out Detection Circuit with Software Disable Function

Reviews

There are no reviews yet.